|

|

|

|

|

低应力空心钨硅通孔阵列助力高密度互连技术发展 Engineering |

|

|

论文标题:Low Stress TSV Arrays for High-Density Interconnection

期刊:Engineering

DOI:https://doi.org/10.1016/j.eng.2023.11.023

微信链接:点击此处阅读微信文章

《Engineering》期刊发表了一篇关于用于高密度互连的低应力空心钨硅通孔(TSV)阵列的研究论文,引发业界关注。该研究由中国科学院微电子研究所焦斌斌团队与西安交通大学韦学勇团队等联合开展,提出了一种新型空心钨 TSV 结构,有望攻克三维(3D)堆叠技术中 TSV 热应力难题,为高密度集成应用发展提供有力支持。

在 3D 集成技术领域,TSV 技术至关重要,它能缩短互连路径、减小封装尺寸,是实现高性能、高集成密度等优势的关键。然而,随着高密度 TSV 阵列的应用,热应力问题日益凸显。由于 TSV 材料与硅的热膨胀系数不同,加工及使用过程中温度变化会导致衬底弯曲、损坏,引发铜挤出、界面分层等一系列可靠性问题,还可能使晶体管迁移率变化、参数漂移,影响性能。传统解决方法是在 TSV 周围设置禁止放置晶体管区域(KOZ),但这浪费了衬底面积,不利于集成度提升。

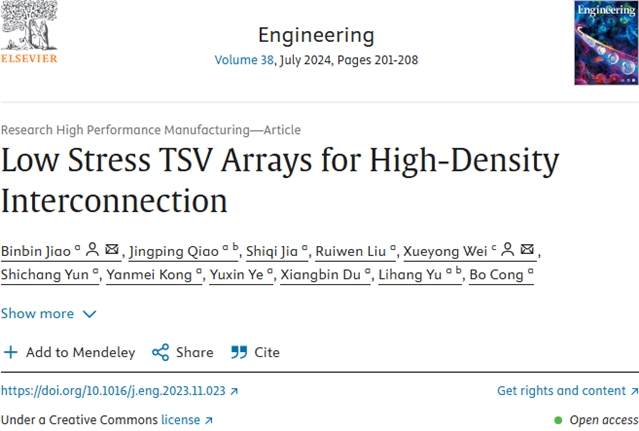

为攻克这一难题,研究团队创新性地提出了空心钨 TSV 方案。其空心结构为热应力释放提供了空间,使应变主要集中在 TSV 内部,减少对硅衬底的影响。通过仿真分析发现,在距衬底表面顶部 2 μm 范围内,空心 W-TSV 可释放 60.3% 的热应力,在 3 μm 径向区域内,热应力可降至 20 MPa 以下。这一性能优于实心 Cu-TSV 和实心 W-TSV,显示出显著的热应力降低效果。

图1 (a)~(c)硅通孔(TSV)模型示意图。(a)实心铜硅通孔(Cu-TSV);(b)实心钨硅通孔(W-TSV);(c)空心钨硅通孔(W-TSV)。(d)~(f)TSV的von Mises应力分布模拟图。(d)实心Cu-TSV;(e)实心W-TSV;(f)空心W-TSV(最大应力分布在金属内部)。

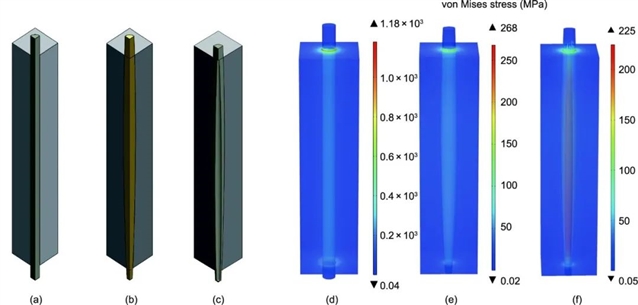

在制造工艺方面,研究团队开发了与 CMOS 兼容的 TSV 最后工艺流程,成功制备了尺寸为 640×512、间距 25 μm、深宽比 20.3∶1 的超高密度(1600 TSV•mm-²)TSV 阵列。制造过程涉及沉积 SiOx硬掩模、干法刻蚀制备 TSV 阵列、优化博世工艺实现特殊形貌、沉积介电层材料、CVD 钨填充等关键步骤。制造出的空心 W-TSV 通孔排列有序,侧壁光滑,金属均匀覆盖,底部无空洞及缺陷,且良品率高,表明 CMOS 制造工艺可用于其生产。

电学性能测试结果显示,单个 TSV 的电阻在 1~1.35 Ω 之间,平均电阻值约 1.21 Ω;在 5 V 时漏电流为 643 pA,变化极小;击穿电压超过 100 V,表明其具有良好的绝缘性能。可靠性测试方面,经过 −40~125 ℃的 100 次温度循环后,电阻变化小于 2%,显示出良好的稳定性。拉曼光谱应力测试表明,空心 W-TSV 在晶圆表面产生的最大应力为 31.02 MPa,远低于其他报道的 TSV 引起的应力,且 2 μm 以外的应力小于 20 MPa,这意味着无需设置 KOZ 区域,有助于高密度集成应用。

图2 (a)TSV阵列的扫描电子显微镜图像;(b)TSV阵列的部分放大扫描电子显微镜图像;(c)单个TSV的扫描电子显微镜图像及TSV参数;(d)空心W-TSV的3D X射线渲染图。

该研究提出的空心钨 TSV 结构在降低热应力、提高电学性能和可靠性方面表现出色,为高密度互连技术发展提供了新的思路和解决方案,有望推动高密度3D集成技术的进一步突破,在近传感器和传感器内计算、混合存储立方体、高带宽存储器(HBM)、互补金属氧化物半导体(CMOS)图像传感器、制冷和非制冷焦平面阵列(FPA)以及有源像素传感器(APS)等领域具有广阔的应用前景。

论文信息:

Binbin Jiao, Jingping Qiao, Shiqi Jia, Ruiwen Liu, Xueyong Wei, Shichang Yun, Yanmei Kong, Yuxin Ye, Xiangbin Du, Lihang Yu, Bo Cong. Low Stress TSV Arrays for High-Density Interconnection. Engineering, 2024, 38(7): 201-208

开放获取:

https://doi.org/10.1016/j.eng.2023.11.023

更多内容

东南大学洪伟教授团队提出双频双极化双工毫米波相控阵概念并完成原型设计及验证

清华团队发布低成本宽带Doherty功放模块,助力5G大规模MIMO基站小型化

让AI更智能,李静海院士团队提出“四一致”新范式

欢迎投票:2025全球十大工程成就评选

Engineering征稿启事:人工智能赋能工程科技

特别声明:本文转载仅仅是出于传播信息的需要,并不意味着代表本网站观点或证实其内容的真实性;如其他媒体、网站或个人从本网站转载使用,须保留本网站注明的“来源”,并自负版权等法律责任;作者如果不希望被转载或者联系转载稿费等事宜,请与我们接洽。