导读

在半导体制造迈向高密度三维堆叠集成电路(3D-IC)的进程中,硅通孔(TSV)等高深宽比结构的质量控制面临严峻挑战 。传统的正面光学检测受制于金属层遮挡与散射,而电子显微技术不仅有损且效率低下 。

针对正面金属层不透光的物理限制,韩国科学技术院(KAIST)联合三星电子,采用背照式(Backside Illumination)策略,即让光线穿透硅衬底“从后方”探测目标 。结合光学频率梳的高精度测距能力,这项基于光梳的背照式新技术,在不破坏芯片的前提下精准测得了内部微孔的深度 。该研究利用 1560 nm 红外光学频率梳,结合色差共焦与光谱干涉技术,成功穿透硅衬底,实现了对晶圆厚度与折射率的同步测量,并对微细 TSV 的深度进行了亚微米级精度的无损表征,为先进封装良率管理提供了全新的无损解决方案 。

该成果以“Backside illumination-enabled metrology and inspection inside 3D-ICs using frequency comb-based chromatic confocal and spectral interferometry”为题发表于Light: Advanced Manufacturing。

定制化红外色差共焦传感系统设计

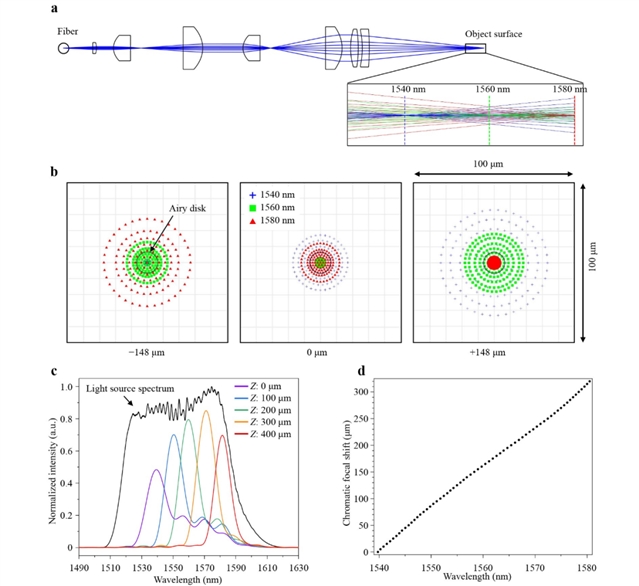

为解决传统可见光手段无法穿透硅衬底以及现有红外传感器带宽过宽导致信号混叠的难题,研究团队构建了基于掺铒光纤光学频率梳的红外色差共焦光谱干涉系统。该系统利用中心波长为1560 nm的光梳作为光源,凭借其低残留强度噪声和高光谱功率密度确保了背侧穿透能力;在传感器端,团队通过光学模拟优化设计了无衍射元件的多级透镜组,在1540~1580 nm波段内实现了296 µm的轴向色差焦移,并在整个测量范围内将光斑尺寸保持在衍射极限水平(约14 µm),从而为高空间分辨率的内部结构成像奠定了坚实的硬件基础。

图1:红外色差共焦传感器设计与性能

厚度/折射率同步解耦与微孔轮廓表征

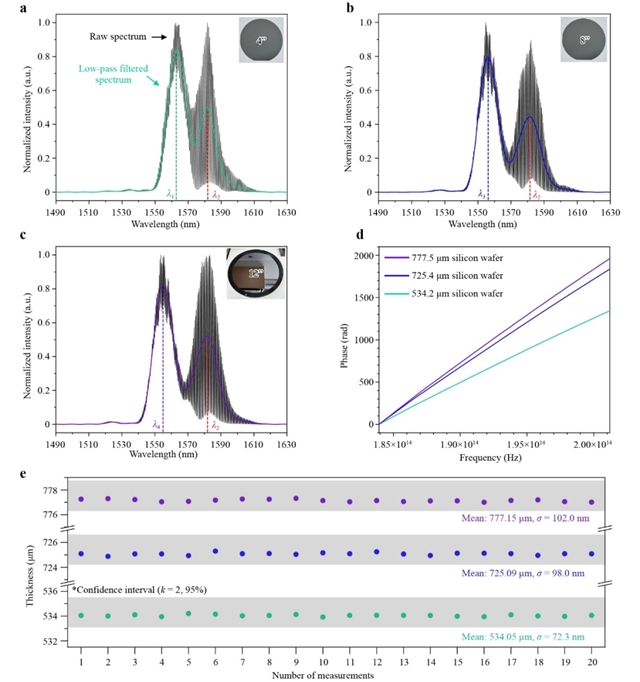

针对硅折射率随工艺条件(如掺杂、温度)波动而导致单一干涉测量存在系统误差的问题,本研究提出了一种无需Z轴机械扫描的同步测量方案。该方法通过数学模型联立色差共焦获取的几何距离信息与光谱干涉获取的光学厚度信息,成功实现了物理厚度与群折射率的同步解算。实验数据显示,在对标称厚度为534.2 µm的硅晶圆进行测试时,该系统不仅消除了折射率非均匀性的影响,更实现了72.3 nm的测量重复性,合成标准不确定度为560.7 nm (k=1),证实了该方法在从“光学厚度”推算“几何真值”方面的极高可靠性。

图2:硅晶圆厚度测量结果

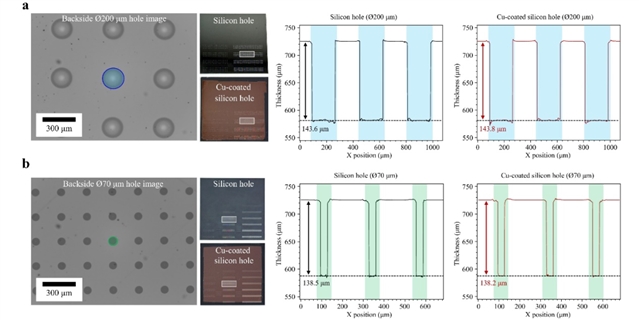

在此基础上,团队进一步验证了该技术对DRIE工艺刻蚀硅孔的检测能力。结合背侧InGaAs成像定位与邻近区域折射率校准,系统有效克服了孔底散射引起的信号衰减,成功测得直径为200 µm和70 µm的硅孔平均深度分别为143.6 µm和138.5 µm,充分证明了该技术对复杂三维微结构进行高精度轮廓表征的鲁棒性。

图3:硅孔样品深度测试结果

工业应用:微细TSV深度的背侧原位检测

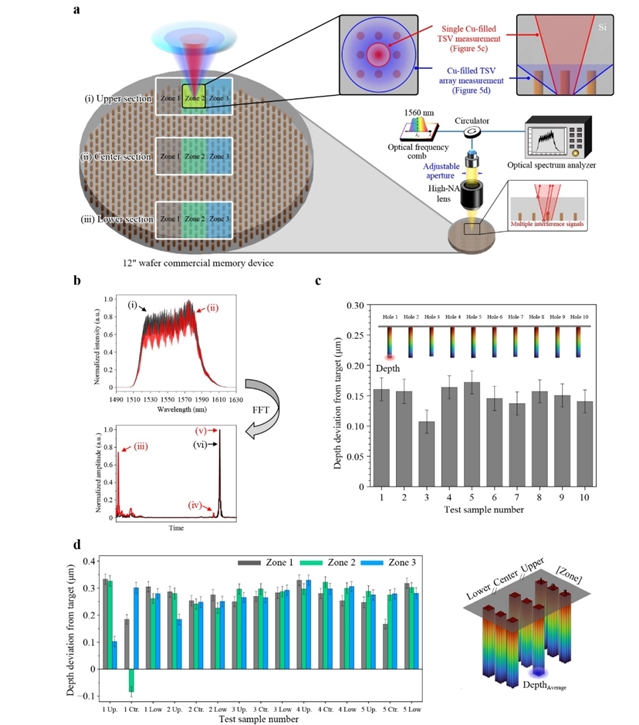

面向直径小于10 µm的微细铜(Cu)填充TSV的检测需求,研究团队通过切换高数值孔径 (NA=0.65) 物镜构建的光谱干涉系统,以解决微小孔底反射信号微弱及信噪比不足的挑战。通过对干涉光谱进行快速傅里叶变换分析,系统能够精准分离TSV底部铜柱与硅表面产生的干涉信号,并在商用12英寸存储器晶圆上完成了全尺度验证。实测结果表明,单个Cu填充TSV的深度测量重复性达18.7 nm,全晶圆阵列的深度最大偏差控制在334 nm以内,完全满足先进封装制程中对TSV深度公差的严苛要求。

图4:Cu填充的TSV深度测量结果

总结与展望

本研究提出的光梳背照技术,通过融合红外光梳、色差共焦与光谱干涉原理,成功攻克了3D-IC背照式检测中“穿透难、精度低、折射率与厚度无法解耦”的核心难题,实现了亚微米级、无损的硅晶圆及TSV深度计量。目前系统单点测量耗时约0.8秒,展望未来,若采用波长色散探测系统(如衍射光栅与线阵相机)并结合GPU加速实时处理算法,有望将采集速率提升至MHz量级,并进一步扩展至晶圆翘曲度测量,从而为后摩尔时代的半导体良率管理与过程控制提供强有力的技术支撑。(来源:先进制造微信公众号)

相关论文信息:https://doi.org/10.37188/lam.2025.074

特别声明:本文转载仅仅是出于传播信息的需要,并不意味着代表本网站观点或证实其内容的真实性;如其他媒体、网站或个人从本网站转载使用,须保留本网站注明的“来源”,并自负版权等法律责任;作者如果不希望被转载或者联系转载稿费等事宜,请与我们接洽。